Makefile

target ... : prerequisites ...

recipe

...

...

-

target

可以是一个 object file(目标文件),也可以是一个可执行文件,还可以是一个标签(label)。对于标签这种特性,在后续的“伪目标”章节中会有叙述。

-

prerequisites

生成该 target 所依赖的文件和/或target。prerequisites中如果有一个以上的文件比target文件要新的话,recipe所定义的命令就会执行

-

recipe

该 target 要执行的命令(任意的shell命令)在 Makefile 中的命令,必须要以

Tab键开始

这就是 makefile 的规则也就是 makefile 中最核心的内容

-

反斜杠 ( \ )是换行符的意思

-

make 是如何工作的

-

make会在当前目录下寻找 Makefile / makefile

-

if finds,它会找第一个目标文件(target), 并把这个文件作为最终的目标文件

-

if it doesn't find target, 或者target所依赖的 .o files 的文件修改时间要比 target 新,它就会执行后面定义的命令来生成target

-

if .o files don't exist , make 会在当前文件寻找目标为 .o 文件的依赖性,如果找到规则就按照该规则生成 .o files (it's similar to the process of stack)

-

bec .c and .h files exist, 于是 make 生成 .o 然后生成make的终极任务

-

-

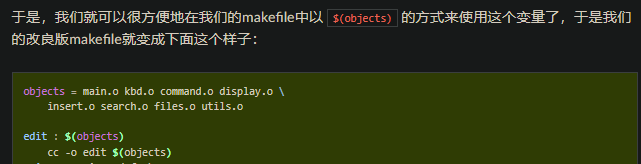

变量 (类似c语言里的宏)

-

自动推导 (其是 make 的隐式规则)

只要 make 看到一个

.o文件,它就会自动的把.c文件加在依赖关系中 -

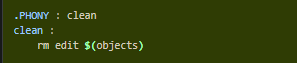

伪目标 (

.PHONY表示clean是个伪目标文件)

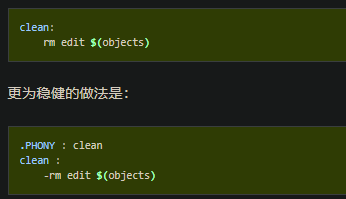

-

清空目录 (在

rm命令前面加小减号是,也许某些文件出现问题,但继续执行 | clean 从来都是放在文件最后)

-

环境变量 MAKEFILES

如果当前环境中定义了环境变量

MAKEFILES,那么make会把这个变量中的值做一个类似于include的动作。这个变量中的值是其它的 Makefile ,用空格分隔。只是,它和include不同的是,从这个环境变量中引入的Makefile的“目标”不会起作用,如果环境变量中定义的文件发现错误,make也会不理。但是在这里我还是建议不要使用这个环境变量,因为只要这个变量一被定义,那么当你使用 make 时,所有的Makefile 都会受到它的影响,这绝不是你想看到的。在这里提这个事,只是为了告诉大家,也许有时候你的 Makefile出现了怪事,那么你可以看看当前环境中有没有定义这个变量。

-

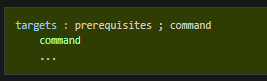

语法

command 是命令行,如果其不与 “targets : prerequisites” 在一行,那么必须以 Tab 开头,如果在一行,用分号间隔

-

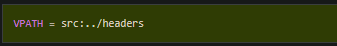

文件搜寻

目录由“冒号”分隔

-

自动生成依赖性

大多数C/C++编译器都支持“-M”的选项,即自动找寻源文件中包含的头文件,并生成一个依赖关系,如果使用GNU的C/C++编译器,你得用

-MM参数,不然,-M参数会把一些标准库的头文件也包含进来